SMARC (“Smart Mobility Architecture”) is a versatile small form factor Computer On Module definition, targeting applications that require low power, low costs and high performance. The Modules will typically use ARM SOCs similar or the same as those used in many familiar devices such as tablet computers and smart phones. Alternative low power SOCs and CPUs, such as tablet oriented X86 devices and other RISC CPUs may be used as well. The Module power envelope is typically under 6W. The Modules are used as building blocks for portable and stationary embedded systems. The core CPU and support circuits, including DRAM, boot flash, power sequencing, CPU power supplies, GBE and a single channel LVDS display transmitter are concentrated on the Module. The Modules are used with application specific Carrier Boards that implement other features such as audio CODECs, touch controllers, wireless devices, etc. The modular approach allows scalability, fast time to market and upgradability while still maintaining low costs, low power and small physical size. The new global standard under the brand name ‘SMARC’ is based on ULP-COM, the term which up to now was used for Ultra Low Power Computer-on-Modules.

Two Module sizes are defined: 82mm x 50mm and 82mm x 80mm. The Module PCBs have 314 edge fingers that mate with a low profile 314 pin 0.5mm pitch right angle connector (the connector is sometimes identified as a 321 pin connector, but 7 pins are lost to the key).

Signal transmission is carried out via a total of 314 pins. 33 of these are reserved signal lines for power supply and grounding, so that with SMARC a total of 281 signal lines are effectively available. ARM- and SoC-typical energy-saving interfaces, like, for instance, parallel LCD for display connection, mobile industry processor interfaces for cameras, Serial Peripheral Interface (SPI) for general peripheral connection, I2S for audio and I2C are included. Besides these, classical computer interfaces such as USB, SATA and PCI Express are also defined.

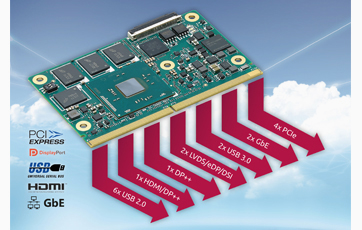

The new computer-on-module standard SMARC 2.0 supports up to four digital displays. A new DP++ (Dual-mode DisplayPort) interface to support resolutions up to Ultra HD/4K with 3840 × 2160 pixels was added. It can be used to connect DisplayPort, HDMI and DVI displays. The single-channel LVDS interface in SMARC 1.1 was upgraded to dual-channel LVDS in 2.0. This interface can drive either two low-resolution or one high-resolution display. Depending on which processor is used, the interface can support up to 1920 x 1200 pixels at 60Hz. Since the HDMI/DP interface remains unaltered, developers can connect up to three high resolution digital displays via modern serial display interfaces. Existing carrier boards with single channel LVDS and HDMI can be used with SMARC 2.0 just as before. Furthermore, the number of USB interfaces has been increased significantly. The SMARC 2.0 standard supports up to six USB 2.0 ports and two USB 3.0 interfaces. Also it supports two GbE interfaces including IEEE1588 trigger signals. Four instead of three PCIe lanes are available for platform-specific extensions, which increases the flexibility for individual function extensions. Three of these PCIe lanes are backward compatible with SMARC 1.1. One of the two SPI buses has been upgraded to eSPI/SPI and instead of triple I2S (I2S2 for HDA option) and SPDIF, 1x I2S (for ARM designs) and 1x HDA (for x86 designs) are now supported. What has not been changed is the support of 1x SATA, 12x GPIO, 2x CAN, 1x SDIO (4bit), 4x UART, 1x HDMI, 1x SPI and 4x I2C.

On April 2020 SMARC SGET committee announced the release of SMARC module Revision 2.1. The Standardization Group for Embedded Technologies, SGET, has just released the new, future-proof specification 2.1. It is fully backward compatible with the current specification 2.0 since the new features can either be multiplexed with existing signals or are additions that do not compromise pins on the edge connector already assigned in the 2.0 specifications.

The major feature updates are:

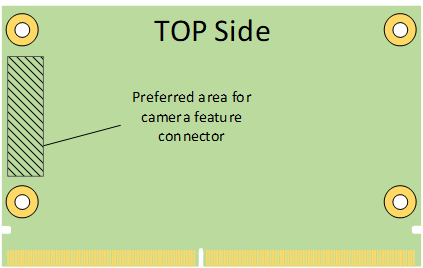

By allowing up to 4 native CSI MIPI camera inputs, the SGET 2.1 specification addresses the fast-growing trend of SOCs that come with integrated Neural Processing Units (NPUs) and multiple camera inputs for video-based AI solutions. The third and fourth camera port are realized through FFC feature connectors on the module itself, each supporting up to 4 MIPI CSI data lanes. Multi camera support is needed for 360-degrees situational awareness for the fast-growing segments such as Robotic vehicles and autonomous driving both of which draw heavily on AI.

The SMARC edge connector pinout already supports two MIPI-CSI rev 2.0/3.0 ports (1x 2-lane, 1x 4-lane). In order to facilitate those AI focused SOCs that provide more MIPI camera ports, an optional feature connector allows for an additional two MIPI CSI rev 2.0/3.0 ports (1x 2-lane, 1x 4-lane).

This will enable a SMARC module to support up to a total of four MIPI CSI rev 2.0/3.0 cameras

The specification update positions SMARC as the preferred standard for scalable, low power, silicon independent AIoM (AI on Module) solutions in the industrial embedded market. To allow multiplexing SERDES signals over the 3rd and 4th PCIe x1 interfaces, is adding the support for an additional two Ethernet ports. This potentially allows a module to work with up to 4 GbE Ethernet ports. These ports can again support the same number of GigE-Vision cameras with a strong focus on AI vision applications.

Besides the above functional changes, the specification itself saw a major structural overhaul to make it more readable. Great attention was given to generate more precise and detailed information about every pin’s power domain and PU/PD status. This effort will simplify carrier board designs and it will increase the level of compatibility and interoperability between module designs, both for different technologies (x86 and ARM) and different vendors.

SMARC clearly stands out as the only truly open, versatile, future proof, low power COM/AIoM standard in a highly fragmented market with a multitude of alternative form factors. Most of these “proprietary alternatives” are either silicon dependent, badly documented, undergoing continuous changes, or are going to be abandoned altogether. As proof of this trend, the SMARC module form factor products are actively being designed and produced by more than 20 leading embedded companies worldwide, with more companies joining in every year.

The complete SMARC module 2.1 specification document is available on the SGeT website (https://sget.org) for a free download.